# 問題1

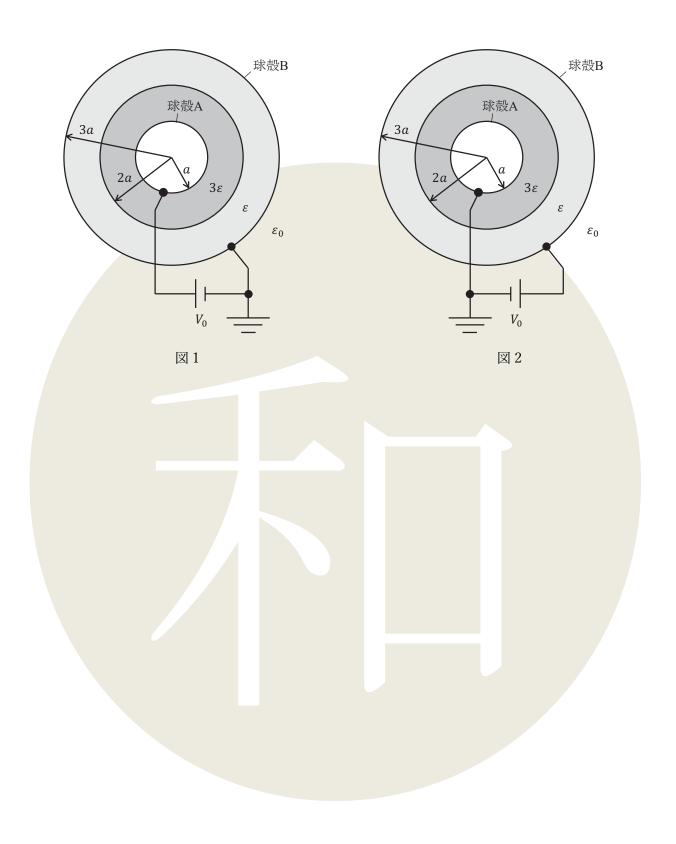

図 1 および図 2 のように、誘電率 $\epsilon_0$ の真空中に半径aと3aの極めて薄い導体球殻 A と B が同心状に置かれ、その間には半径2aの同心球面を境に誘電率 $3\epsilon$ と $\epsilon$ の誘電体が満たされている。ここで、球殻 A の電荷を $q_A$ とする。ただし、問(3)–(7)では解答に $q_A$ を用いてはならない。また、無限遠の電位を0とする。

まず、図1のように球殻Bを接地し、球殻Aに電圧 $V_0$ (>0)を印加した。以下の問に答えよ。

- (1) 球殻の中心から距離rにおける電界の大きさを、 $q_A$ を用いて表せ.

- (2)  $q_A \, \mathcal{V}_0$ の関係を求めよ.

- (3) 球殻の中心から距離rにおける電位を求め、rに対する電位のグラフを描け、

- (4) 仮想変位を用いて、球殻 B に働く単位面積当たりの静電気力の大きさと向きを求めよ.

次に、図 2 のように球殻 A を接地し、球殻 B に電圧 $V_0$  (> 0)を印加した. 以下の間に答えよ.

- (5) 球殻 B の電荷および、誘電体の半径3aの表面の分極電荷密度を求めよ.

- (6) 球殻の中心から距離rにおける電界のエネルギー密度を求めよ. また, この電界のエネルギー密度を用いて, この系に蓄えられた静電エネルギーを求めよ.

- (7) 球殻 B から離れた位置に、新たに半径aの導体球 C を置き、導体球 C に電圧 $-2V_0$ を印加した。球殻 B と導体球 C の中心間距離が10aのとき、電気力線の概略を描け、球殻 B の内側の電気力線も描くこと。ただし $\epsilon=2\epsilon_0$ とする。

### **Problem 1**

As shown in Figs. 1 and 2, infinitely thin spherical conducting shells A and B of radii a and 3a, respectively, are concentrically placed in vacuum of permittivity  $\varepsilon_0$ , and dielectric substances of permittivity  $3\varepsilon$  and  $\varepsilon$  are inserted between shells A and B with a sphere of radius 2a as a boundary. The electric charge on shell A is denoted by  $q_A$ . Do not use  $q_A$  for answers in Questions (3)–(7). Let the potential at infinity be zero.

First, as shown in Fig. 1, shell B is grounded and voltage  $V_0$  (> 0) is applied to shell A. Answer the following questions.

- (1) Express the electric field strength at a distance r from the center of the spherical shells using  $q_A$ .

- (2) Find the relation between  $q_A$  and  $V_0$ .

- (3) Find the potential at a distance r from the center of the spherical shells, and plot the potential as a function of r.

- (4) Find the magnitude and direction of electrostatic force per unit area acting on shell B using the principle of virtual work.

Next, as shown in Fig. 2, shell A is grounded and the voltage  $V_0$  (> 0) is applied to shell B. Answer the following questions.

- (5) Find the electric charge on shell B and the polarization charge density on the surface of the dielectric substance at radius 3a.

- (6) Find the electric energy density at a distance r from the center of the spherical shells. Then, calculate the electrostatic energy stored in this system using the electric energy density.

- (7) A conducting sphere C of radius a is newly placed at a distance from shell B, and voltage  $-2V_0$  is applied to sphere C. Sketch the electric lines of force when the distance between the centers of shell B and sphere C is 10a. Do not forget to include the lines that are inside shell B. Let  $\varepsilon = 2\varepsilon_0$ .

### 問題2

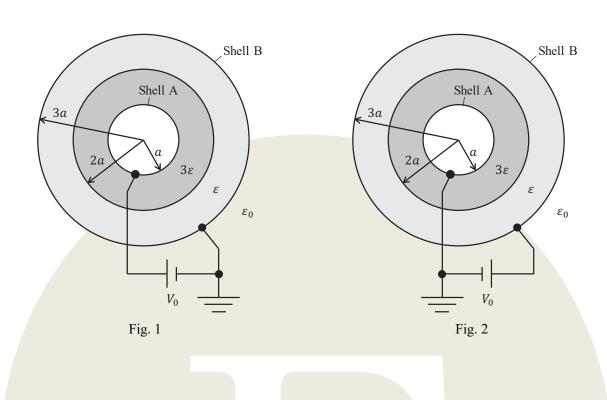

- I. 線形回路に関する以下の問に答えよ. なお、jを虚数単位とする.

- 図1の回路における端子対 A-A', B-B'間の電圧伝達関数 $H(j\omega)$ を角周波数 $\omega$ の関数 として求めよ.

- (2) 問(1)で求めた $H(j\omega)$ の振幅および位相を導出し、その角周波数依存性の概形(ボード線図)を図示せよ。なお、振幅および角周波数は対数軸を使用し、位相は線形軸を使用すること。また、 $L=1\,\mathrm{H},\ C=1\,\mathrm{F},\ R_1=1\,\Omega,\ R_2=1\,\Omega$ とせよ。

- (3) 図 2 に示すように、端子 A-A'に電圧入力 $V_{in1}(t)$ を加えたとき、端子 B-B'で観測される電圧過渡応答 $V_{out1}(t)$ を求め、図示せよ、なお、L=1 H、C=1 F、 $R_1=1$   $\Omega$ 、 $R_2=1$   $\Omega$ とせよ、

- (4) 図 2 において、L=x [H]、C=1 F、 $R_1=1$   $\Omega$ 、 $R_2=1$   $\Omega$ とするとき、端子 B-B'で観測される電圧過渡応答に振動成分が生じないxの範囲を求めよ.

- 図3に示すように端子 A-A'に正弦波交流電流 $I_{\rm in2}(t)=\sqrt{2}I_2\cos\omega t$ を加えたとき、端子 A-A'に生じる電圧  $V_2(t)$ を求め、電流源が供給する有効電力P、無効電力Q(ただし遅れを正とする)、皮相電力S、および、このときの力率PFを求めよ.

II. n 型 MOS トランジスタを用いたソース接地増幅回路に関する以下の問に答えよ. なお、MOS トランジスタの小信号等価回路は、必要に応じて図 4 (a)もしくは図 4 (b)を用いること. ただし、 $g_{\rm m}$ 、 $r_{\rm o}$ 、 $g_{\rm mb}$ はそれぞれ n 型 MOS トランジスタの相互コンダクタンス、ドレイン抵抗、基板コンダクタンス(基板バイアス電圧に関する相互コンダクタンス)を表す.

- (6) 図5に示す抵抗負荷型ソース接地増幅回路の小信号等価回路を図示せよ.

- (7) 問(6)の電圧増幅率 $A_{v1} = \frac{v_{\text{out1}}}{v_{\text{in1}}}$ および出力端子 $V_{\text{out1}}$ から見た回路の出力抵抗 $R_{\text{out1}}$ を求めよ。ただし、 $v_{\text{in1}}$ 、 $v_{\text{out1}}$ はそれぞれ入力 $V_{\text{in1}}$ ,出力 $V_{\text{out1}}$ の小信号成分である。

- (8) 理想的な定電流源を用いた図 6 の定電流源負荷型ソース接地増幅回路について考える。この回路の電圧増幅率 $A_{v2}=\frac{v_{\text{out2}}}{v_{\text{in2}}}$ を求めよ。ただし、 $v_{\text{in2}}$ 、 $v_{\text{out2}}$ はそれぞれ入力 $V_{\text{in2}}$ 、出力 $V_{\text{out2}}$ の小信号成分とする。

- (9) 定電流源は、実際には理想的な定電流源の代わりに、図 7 に示すように MOS トランジスタを用いて実現されることが多い。図 7 の回路における電圧増幅率 $A_{v3} = \frac{v_{out3}}{v_{in3}}$ を求めよ。ただし、 $v_{in3}$ 、 $v_{out3}$ はそれぞれ入力 $V_{in3}$ 、出力 $V_{out3}$ の小信号成分であり、 $V_{b3}$ は適当なバイアス電圧とする。また、図 7 で用いた n 型 MOS、p 型 MOS の相互コンダクタンス $g_{m}$ 、ドレイン抵抗 $r_{o}$ 、基板コンダクタンス $g_{mb}$ はいずれも同じであるとする。必要なものを用いて答えよ。

- (10)  $A_{v1}$ ,  $A_{v2}$ ,  $A_{v3}$ の大きさを比較せよ. また、その理由を3行程度で述べよ.

凡例

#### **Problem 2**

- I. Answer the following questions related to linear circuits. Here, j is the imaginary unit.

- (1) Concerning the circuit in Fig. 1, find the voltage transfer function  $H(j\omega)$  between terminal pairs A-A' and B-B' as a function of angular frequency  $\omega$ .

- (2) Assuming L=1 H, C=1 F,  $R_1=1$   $\Omega$ , and  $R_2=1$   $\Omega$ , find the amplitude and the phase of  $H(j\omega)$  derived in Question (1), and draw them as functions of  $\omega$  (Bode diagram). Use logarithmic axes for the amplitude and the angular frequency, and linear axis for the phase.

- (3) As shown in Fig. 2, let us assume a voltage source  $V_{\text{in1}}(t)$  at the terminal A-A'. Find the voltage transient response  $V_{\text{out1}}(t)$  appearing at the terminal B-B', and draw it, assuming L = 1 H, C = 1 F,  $R_1 = 1$   $\Omega$ , and  $R_2 = 1$   $\Omega$ .

- (4) Assuming L = x [H], C = 1 F,  $R_1 = 1$   $\Omega$ , and  $R_2 = 1$   $\Omega$  in Fig. 2, find the range of x, where the transient response appearing at the terminal B-B' contains no oscillation component.

- (5) Let us assume a sinusoidal current  $I_{\text{in2}}(t) = \sqrt{2}I_2 \cos \omega t$  at the terminal A-A', as shown in Fig. 3. Find the voltage  $V_2(t)$  appearing at the terminal A-A'. Also find the active power P, the reactive power Q (defined as positive in the case of lag), the apparent power S, which are supplied by the current source, and the power factor PF.

II. Answer the following questions related to the common source amplifier that consists of an n-type MOS transistor. Note that a small signal equivalent circuit of a transistor is expressed as either Fig. 4(a) or Fig. 4(b). Here,  $g_{\rm m}$ ,  $r_{\rm o}$ , and  $g_{\rm mb}$  are transconductance of MOS transistor, drain resistance, and body conductance (transconductance according to body bias voltage), respectively.

- (6) Draw a small signal equivalent circuit of the common source amplifier with resistive load shown in Fig. 5.

- (7) Find the voltage gain  $A_{v1} = \frac{v_{out1}}{v_{in1}}$  and output resistance  $R_{out1}$  appearing at output  $V_{out1}$  in the circuit in Question (6). Note that  $v_{in1}$  and  $v_{out1}$  represent small signal components of the input  $V_{in1}$  and the output  $V_{out1}$ , respectively.

- (8) Consider the common source amplifier with the ideal constant current-source load shown in Fig. 6. Find the voltage gain  $A_{v2} = \frac{v_{out2}}{v_{in2}}$ . Note that  $v_{in2}$  and  $v_{out2}$  represent small signal components of the input  $V_{in2}$  and the output  $V_{out2}$ , respectively.

- (9) In reality, the constant current source is often realized by MOS transistor shown in Fig. 7, instead of the ideal constant current source. Find the voltage gain  $A_{\rm v3} = \frac{v_{\rm out3}}{v_{\rm in3}}$ . Note that  $v_{\rm in3}$  and  $v_{\rm out3}$  represent small signal components of the input  $V_{\rm in3}$  and the output  $V_{\rm out3}$ , respectively, and  $V_{\rm b3}$  represents the appropriate bias voltage. Note that n-type MOS and p-type MOS in Fig. 7 have the same transconductance  $g_{\rm m}$ , drain resistance  $r_{\rm o}$ , and body conductance  $g_{\rm mb}$ . Use these parameters as necessary in your answer.

- (10) Compare the magnitudes of  $A_{v1}$ ,  $A_{v2}$ , and  $A_{v3}$ , and describe the reason of the magnitude relation in about three lines.

Legend

# 問題3

$F = \{0,1,2,3\}$ を入力・出力に持つ通信路 $\mathcal{E}$ を考える。ある入力 $x \in \mathcal{F}$ に対し、ある出力 $y \in \mathcal{F}$ が得られる確率P(y|x)を

$$P(y|x) = \begin{cases} p(1-q) & : y = x \text{ の場合} \\ (1-p)q & : y = (x+1) \text{ mod } 4 \text{ の場合} \\ (1-p)(1-q) & : y = (x+2) \text{ mod } 4 \text{ の場合} \\ pq & : y = (x+3) \text{ mod } 4 \text{ の場合} \end{cases}$$

と定める. ここで $a \mod b$ はbによるaの剰余演算を意味し,  $0 \le p \le 1$ ,  $0 \le q \le 1$ とする. 対数 $\log o$  底は2, 通信路 $\mathcal{E}$ の通信路容量を $\mathcal{E}$ とする. 以下の間に答えよ.

- (1) q = 1の場合について通信路 $\varepsilon$ の通信路線図を図示せよ.

- (2) 通信路 $\varepsilon$ について、入力がxに固定された時の出力のエントロピーをpとqの関数として求めよ。

- (3) 通信路容量Cをpとqの関数C(p,q)として求めよ.

- (4) C(p,q)の最小値、および最小値を与えるすべてのpとqの組を求めよ。また、なぜそのようなpとqの組で通信路容量が最小となるか、理由を 2 行程度で述べよ。

- (5) C(p,q)の最大値、および最大値を与えるすべてのpとqの組を求めよ。また、なぜそのようなpとqの組で通信路容量が最大となるか、理由を 2 行程度で述べよ。

- (6) p+q=1/2とするとき、C(p,q)の最大値、および最大値を与えるすべてのpとqの組を求めよ、導出も記すこと、

- (7)  $\mathcal{A} = \{a, b, c, d\}$ を通信路 $\mathcal{E}$ を使って送ることを考える。 $\mathcal{A}$ の 1 文字を $\mathcal{F}$ の 2 文字で符号化する。p = 1/2およびq = 1とするとき、誤りを最小化する符号の割当をひとつ求めよ。ただし、 $a \to 00$ は固定とする。また、求めた符号の割当と通信路容量との関係を2 行程度で述べよ。

#### **Problem 3**

Suppose that  $\mathcal{E}$  is an information transmission channel whose input and output are taken from  $\mathcal{F} = \{0,1,2,3\}$ . Let P(y|x) be the probability to have an output  $y \in \mathcal{F}$  given an input  $x \in \mathcal{F}$ , which is defined as

$$P(y|x) = \begin{cases} p(1-q) & : \text{ when } y = x, \\ (1-p)q & : \text{ when } y = (x+1) \text{mod } 4, \\ (1-p)(1-q) & : \text{ when } y = (x+2) \text{mod } 4, \\ pq & : \text{ when } y = (x+3) \text{mod } 4, \end{cases}$$

where  $a \mod b$  is modulo of a by b,  $0 \le p \le 1$ , and  $0 \le q \le 1$ . Let the base of log be 2 and C be the channel capacity of the channel  $\mathcal{E}$ . Answer the following questions.

- (1) Draw the channel diagram of the channel  $\mathcal{E}$  for q = 1.

- (2) For the channel  $\mathcal{E}$ , express the entropy of the output as a function of p and q when the input is fixed to x.

- (3) Express the channel capacity C as a function of p and q: C(p,q).

- (4) Find the minimum of C(p,q) and all the pairs of p and q that attain the minimum. Also describe the reason, in about two lines, why those pairs of p and q attain the minimum.

- (5) Find the maximum of C(p,q) and all the pairs of p and q that attain the maximum. Also describe the reason, in about two lines, why those pairs of p and q attain the maximum.

- (6) When p + q = 1/2, find the maximum of C(p,q) and all the pairs of p and q that attain the maximum. Write down the derivation as well.

- (7) Suppose that we send  $\mathcal{A} = \{a, b, c, d\}$  by using the channel  $\mathcal{E}$ . We encode each letter of  $\mathcal{A}$  by two letters of  $\mathcal{F}$ . When p = 1/2 and q = 1, derive a mapping that minimizes the transmission error, provided that  $a \to 00$  is fixed. Also, describe the relationship between the derived mapping and the channel capacity in about two lines.

# 問題4

n 個の整数からなるデータ列を data とする. プログラム 1 は sort(data, 0, n-1) と呼び出すことによって data を昇順にソートする C 言語の関数である. ここで data の要素はすべて異なる値を持つものとする. 以下の問に答えよ.

```

/* プログラム1 */

void sort(int data[], int left, int right){

if(left < right){</pre>

int pivot = data[right];

int pos = left;

int i, tmp;

for(i = left; i < right; i++){}

if(data[i] < pivot){</pre>

tmp = data[pos]; data[pos] = data[i]; data[i] = tmp;

pos++;

}

tmp = data[pos]; data[pos] = data[right]; data[right] = tmp;

sort(

(i)

sort(

(ii)

}

```

- (1) このソートアルゴリズムを3行程度で説明せよ.

- (2) プログラム 1 の(i)および(ii)に対応するコードを C 言語で記述せよ.

- (3) 要素数 n に対するこのアルゴリズムの最大計算量のオーダーおよび平均計算量のオーダーを求めよ. この際, データの比較回数のみを考えればよい.

- (4) どのような場合に最大計算量となるか、対象となるデータおよび基準値 pivot の選択 の観点からそれぞれ説明せよ.

以下の問ではそれぞれプログラム1を改変するものとする.

- (5) 基準値 pivot の選び方を工夫することによって計算を効率化したい. 考えられる効率 化手法をひとつ, 理由とともに 3 行程度で説明せよ.

- (6) 再帰計算の代わりにスタックを用いてプログラム1のアルゴリズムを実装したい. 関数は sort\_stack(data, n)と呼び出すものとする. また, ただちにソートを行わない区間の左右の位置をスタックにプッシュするものとする. このソートアルゴリズムのプログラムを C 言語で記述せよ. プログラム中で改変しない部分は省略してもよい. スタックのデータ構造および push, popの関数は適切に定義せよ.

#### **Problem 4**

Let data be a data array of n integers. Program 1 is a function, written in the C programming language, to sort data in ascending order by calling sort(data, 0, n - 1). Assume that all elements in data have different values. Answer the following questions.

- (1) Explain this sort algorithm in about three lines.

- (2) Write codes appropriate for blanks (i) and (ii) in Program 1 by using the C programming language.

- (3) Give the maximum and average orders of the time complexity of the algorithm for the number of elements n. You may consider only the number of comparisons of the values.

- (4) Describe the situations when the order of the time complexity becomes maximum by considering the given data and the selection of the reference value pivot, respectively.

We will modify Program 1 in the following questions, respectively.

- (5) We want to improve the computational efficiency by modifying the selection method of the reference value pivot. Describe one possible method to achieve this, with reasoning, in about three lines.

- (6) We want to implement the algorithm of Program 1 by using the stack instead of the recursive computation. Assume that we call the function as sort\_stack(data, n). Also, assume that the left and the right positions of a data array not to be sorted immediately are pushed to the stack. Write a program of this sort algorithm by using the C programming language. You may omit the lines of the program that are not modified from Program 1. Define the data structure of the stack and the functions push and pop appropriately.

# 問題A

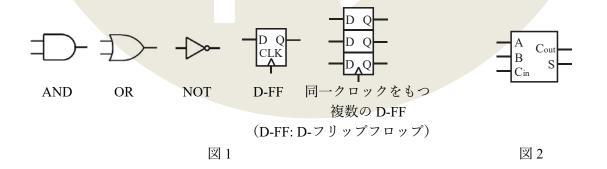

- I. 論理回路について、以下の間に答えよ、回路図では、三つ以上の入力数をもつ AND、OR も用いてよい、また、入力値を 0 または 1 に固定するときは、"0" または "1"と入力に記載せよ、

- (1) 1 ビットの入力 A, B の和 S と,繰り上がり  $C_{out}$  を出力する半加算器の回路を図 1 の記号を用いて図示せよ.

半加算器は下位の桁からの繰り上がりを受け取れない。下位の桁からの繰り上がりを足し込む機能をもつ加算器を全加算器という。

- (2) 問(1)の半加算器の入出力に加えて、下位の桁からの繰り上がり入力  $C_{in}$  をもつ全加算器の真理値表を作成せよ。カルノー図を用いて全加算器の  $C_{out}$  を出力する回路を設計し、その回路を図 1 の記号を用いて図示せよ。

- (3) 全加算器を図 2 の記号で表すこととする.1 ビットの入力信号 I と 3 ビットの出力信号  $O_2O_1O_0$  をもつ回路を考える.入力 I が 0 から 1 に変化するごとに,出力  $O_2O_1O_0$  が,(a) もしくは(b)のように順に変化する.それぞれの回路を図 1 と図 2 の記号を用いて図示せよ.すべての D-FF のクロック入力 CLK に入力 I を接続することとする.

(a)

$$\rightarrow 000 \rightarrow 001 \rightarrow 010 \rightarrow 011 \rightarrow 100 \rightarrow 101 \rightarrow 110 \rightarrow 111$$

(b)

$$> 000 \rightarrow 001 \rightarrow 010 \rightarrow 011 \rightarrow 100 \rightarrow 101 \rightarrow 110 \rightarrow 111 \rightarrow 110 \rightarrow 101 \rightarrow 100 \rightarrow 011 \rightarrow 010 \rightarrow 001$$

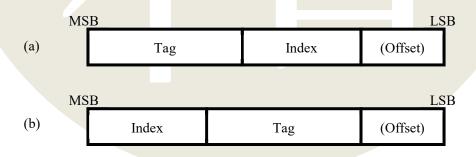

- II. 4M 語の主記憶アドレス空間と、32K 語の単一のキャッシュメモリをもつ計算機を考える。主記憶の内容は32 語の大きさのブロック単位でキャッシュされるものとする。キャッシュ上のそれぞれのブロックはタグ(Tag)領域をもつ。このキャッシュメモリのタグ領域は、主記憶アクセス時にアクセスアドレスのタグ部と照合される。必要なタグの照合は、主記憶アクセス毎に並列に行われるものとする。1M は $2^{20}$ , 1K は $2^{10}$ とする。解答には $2^{10}$ のべき乗表記を用いてよい。以下の間に答えよ。

- (4) キャッシュメモリは何ブロックからなるか答えよ. また,主記憶のアドレス空間は何ブロックに相当するか答えよ.

- (5) 主記憶上のブロックを任意のブロックに格納できるキャッシュメモリを考える.

- A) タグのビット数を答えよ.

- B) タグを照合する比較器がキャッシュメモリシステム全体で何個必要か答えよ.

- C) このようなキャッシュメモリの方式の名称を答えよ.

- (6) 主記憶上の各ブロックが、それぞれ対応するひとつのブロックにしか格納できないキャッシュメモリを考える。主記憶上のアドレスのうちインデックス(Index)部によりキャッシュメモリ上のどのブロックに格納されるかが決まる。

- A) タグとインデックスそれぞれのビット数を答えよ.

- B) タグを照合する比較器はキャッシュメモリシステム全体で何個必要か答えよ.

- C) このようなキャッシュメモリの方式の名称を答えよ.

- (7) 図 3 は主記憶のアドレスへのタグとインデックスの割り当てを示している. 問(6)の場合, キャッシュのヒット率を上げるには, 図 3 の(a), (b)のどちらの割り当てがよいか, 理由とともに論ぜよ.

MSB: most significant bit LSB: least significant bit

### **Problem A**

- I. Answer the following questions on logic circuits. In circuit diagrams, you may use AND and OR which have three or more inputs. To fix an input value to 0 or 1, put "0" or "1" at the input.

- (1) Using the symbols in Fig. 1, draw a circuit of a half adder, which outputs sum S and carry C<sub>out</sub> of 1-bit inputs A and B.

A half adder cannot receive a carry from the lower digit. An adder that can add a carry from the lower digit is called a full adder.

- (2) Give the truth table of a full adder that has an input C<sub>in</sub> for the carry from the lower digit, in addition to the inputs and outputs of the half adder in Question (1). Design a circuit that gives C<sub>out</sub> of the full adder using a Karnaugh map, and draw the circuit using the symbols in Fig. 1.

- (3) The symbol in Fig. 2 represents a full adder. Consider a circuit with a 1-bit input signal I and a 3-bit output signal O<sub>2</sub>O<sub>1</sub>O<sub>0</sub>. The output O<sub>2</sub>O<sub>1</sub>O<sub>0</sub> changes in the order as shown in (a) or (b) every time when the input I changes from 0 to 1. Draw the circuits for the respective cases by using the symbols in Fig. 1 and Fig. 2. The clock inputs CLK of the all D-FF must be connected to the input I.

(a)

$$\geqslant 000 \rightarrow 001 \rightarrow 010 \rightarrow 011 \rightarrow 100 \rightarrow 101 \rightarrow 110 \rightarrow 111$$

(b)

$$\geqslant 000 \rightarrow 001 \rightarrow 010 \rightarrow 011 \rightarrow 100 \rightarrow 101 \rightarrow 110 \rightarrow 101 \rightarrow 100 \rightarrow 011 \rightarrow 010 \rightarrow 001$$

- II. Consider a computer with a 4M-word main memory address space and a 32K-word single cache memory. The main memory is cached in the unit of the 32-word cache block. Each block in the cache has a Tag field. The Tag field of a cache block is checked against the Tag part of the access address when the main memory is accessed. We assume that required Tag field comparison is performed in parallel for each main memory access. Here, 1M is 2<sup>20</sup>, and 1K is 2<sup>10</sup>. You may use power-of-two representations in the answer. Answer the following questions.

- (4) Give the number of blocks in the cache memory, and the number of blocks that the main memory address space corresponds to.

- (5) Consider a cache memory in which a block in the main memory can be cached at any block.

- A) Give the number of bits of a Tag.

- B) Give the number of comparators required in the entire cache memory system to check the Tag part.

- C) Give the name of this type of cache memory.

- (6) Consider a cache memory in which each block in the main memory can only be cached at a corresponding block. The Index part of the address of the main memory determines the block in the cache memory at which the block in the main memory is stored.

- A) Give the number of bits of a Tag and an Index.

- B) Give the number of comparators required in the entire cache memory system to check the Tag part.

- C) Give the name of this type of cache memory.

- (7) Fig. 3 shows allocations of the Tag and the Index in a main memory address. In the case of Question (6), which one of (a) and (b) is better to make the cache hit rate higher? Discuss with the reason.

MSB: most significant bit LSB: least significant bit

Fig. 3

# 問題B

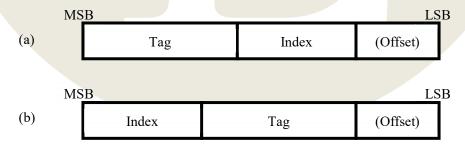

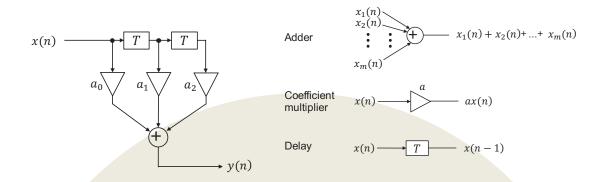

図 1 に示す有限インパルス応答 (FIR: finite impulse response) システムを考える. ただし,  $n=0,1,\cdots$ として, x(n)とy(n)はそれぞれ入力信号系列と出力信号系列であり, 時刻nT (T>0)における信号値を表す. 回路は, 加算器, 係数乗算器, および, 時間Tの遅延器から構成され, それぞれの働きは図 2 に示す通りである. 図 1 中の $a_m$  (m=0,1,2) は各係数乗算器の係数を表し, 実数とする.

以下の問に答えよ。ただし、問中の $\omega$ は角周波数、jは虚数単位を表す。

- (1)  $a_0 = 1/4$ ,  $a_1 = 1/2$ ,  $a_2 = 1/4$ の場合を考える.

- (a) このシステムのインパルス応答 $h_1(n)$ と、そのz変換 $H_1(z)$ を求めよ.

- (b) このシステムの周波数応答を $A(\omega)e^{j\theta(\omega)}$ と書く、ただし、 $A(\omega)$ と $\theta(\omega)$ は、 $\omega$ の実関数である、このシステムは直線位相特性を持つ、すなわち、 $\theta(\omega)$ が $\theta(\omega) = D\omega + \theta_0$ の形で表されることを示し、Dと $\theta_0$ を求めよ、また、 $A(\omega)$ を求め、 $\omega$ に対してプロットせよ、

- (c) このシステムが入力信号に対して行うフィルタリング機能を2行程度で説明せよ.

- (2) 図 1 の FIR システムが直線位相特性を持つための $a_m$  (m=0,1,2) の条件を求めよ. ただし、 $a_m$ のうち少なくとも 2 つは非零であるとする.

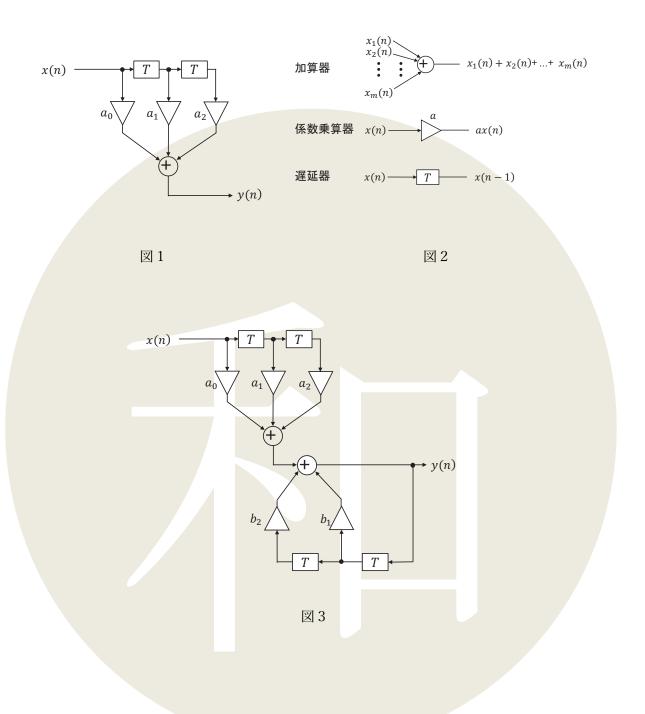

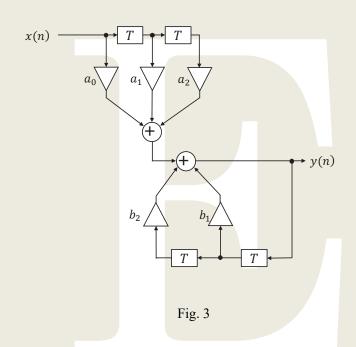

次に、図3に示す再帰型システムを考える。ただし、 $a_0$ 、 $a_1$ 、 $a_2$ 、 $b_1$ 、 $b_2$ は各係数乗算器の係数を表し、実数とする。

- (3) このシステムのインパルス応答のz変換 $H_2(z)$ を求めよ.

- (4)  $a_0 = 1$ ,  $a_1 = 4$ ,  $a_2 = 4$ ,  $b_2 = 0$ のとき、この系が安定であるための $b_1$ の条件を求めよ.

- (5)  $a_0 = -b_2$ ,  $a_1 = -b_1$ ,  $a_2 = 1$ の場合を考える. ただし, 0 < r < 1, かつ,  $0 として, <math>H_2(z)$  の 2 つの極が  $z = re^{\pm jp}$  と表されるとする.

- (a) このシステムの零点をrとpを用いて表せ.

- (b) このシステムが入力信号に対して行うフィルタリング機能を説明せよ. 導出も記すこと.

- (6) 図3の回路は、線形なシステムであるため、幾つかの異なる構成に変形することができる。図3の回路と同じ応答特性を持ちながら、遅延器の数を削減した回路を一つ図示せよ。

### **Problem B**

Consider the finite impulse response (FIR) system shown in Fig. 1. Here, x(n) and y(n) are the input and output signal sequences, respectively, and represent the signal values at time nT (T > 0) for  $n = 0, 1, \cdots$ . The circuit consists of an adder, coefficient multipliers, and delays of T, whose respective functions are described in Fig. 2. In Fig. 1,  $a_m$  (m = 0, 1, 2) represent the coefficients of respective multipliers and have real values.

Answer the following questions. In the questions,  $\omega$  denotes the angular frequency, and j is the imaginary unit.

- (1) Consider the case where  $a_0 = 1/4$ ,  $a_1 = 1/2$ , and  $a_2 = 1/4$ .

- (a) Derive the impulse response of this system  $h_1(n)$  and its z-transform  $H_1(z)$ .

- (b) Let the frequency response of this system be expressed as  $A(\omega)e^{j\theta(\omega)}$ , where  $A(\omega)$  and  $\theta(\omega)$  are real-valued functions of  $\omega$ . Show that this system has a linear-phase property, or in other words,  $\theta(\omega)$  is expressed in the form  $\theta(\omega) = D\omega + \theta_0$ . Derive D and  $\theta_0$ . Also, obtain the expression for  $A(\omega)$  and plot it as a function of  $\omega$ .

- (c) Explain the filtering function of this system on the input signal in about two lines.

- (2) Derive the conditions of  $a_m$  (m = 0, 1, 2) for the FIR system in Fig. 1 to have a linear-phase property. Assume that at least two of  $a_m$  are non-zero.

Next, consider the recursive system shown in Fig. 3. Here,  $a_0$ ,  $a_1$ ,  $a_2$ ,  $b_1$ , and  $b_2$  represent the coefficients of respective multipliers, and are real values.

- (3) Derive the z-transform  $H_2(z)$  of the impulse response for this system.

- (4) Consider the case where  $a_0 = 1$ ,  $a_1 = 4$ ,  $a_2 = 4$ , and  $b_2 = 0$ . Derive the condition of  $b_1$  for this system to be stable.

- (5) Consider the case where  $a_0 = -b_2$ ,  $a_1 = -b_1$ , and  $a_2 = 1$ . Assume that the two poles of  $H_2(z)$  are expressed as  $z = re^{\pm jp}$ , where 0 < r < 1 and 0 .

- (a) Express the zero(s) of this system by using r and p.

- (b) Explain the filtering function of this system on the input signal. Write down the derivation as well.

- (6) Since the circuit in Fig. 3 is a linear system, it can be rearranged into several different configurations. Draw a circuit with a fewer number of delays while the response is the same as that of the circuit shown in Fig. 3.

Fig. 1 Fig. 2

# 問題C

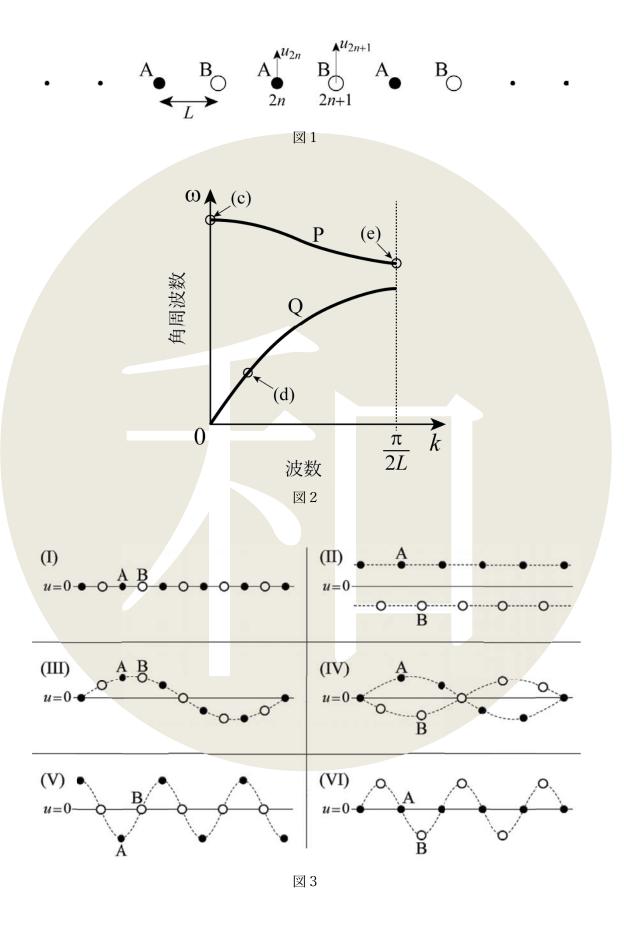

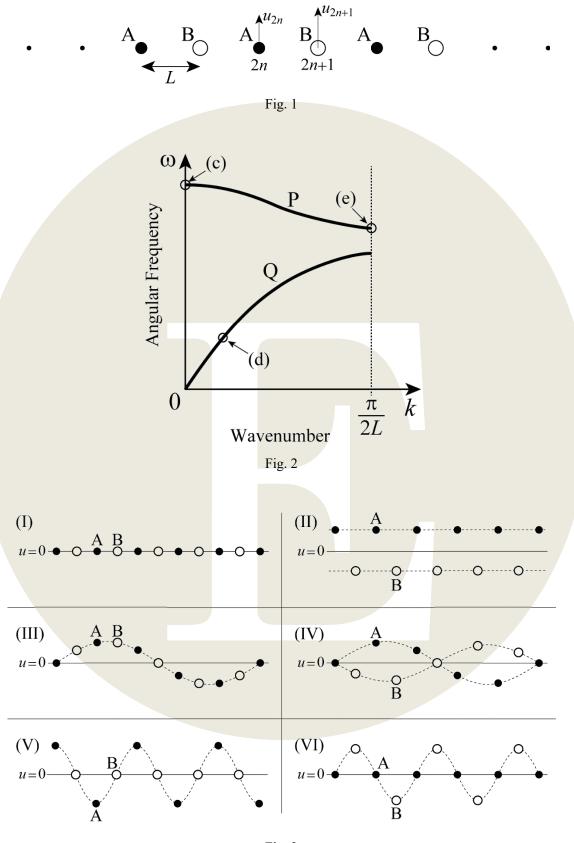

固体中の格子振動(フォノン)について,図1に示すような原子 A と B が間隔 L で並んだ一次元格子のモデルで考える.ここで,A と B の質量を,それぞれ,m と M とし,また,m < M であるとする.ここでは横波型の格子振動を考え,各原子 A,B の平衡位置からの横方向変位をそれぞれ $u_{2n}$ ,  $u_{2n+1}$  (nは整数)のように表す.また,各隣接原子間にのみフックの法則(バネ定数  $\beta$ )に従った力が働き,例えば,2n番目と2n+1番目の原子の間に働く力の大きさは  $\beta(u_{2n+1}-u_{2n})$  で表されるものとする.このとき,以下の間に答えよ.

- (1) 横波のフォノンにおける角周波数  $\omega$  と波数 k の分散曲線としては、図 2 の P, Q のような 2 種類がある。図 2 の(c), (d)の状態における原子の最大変位の概略を示すものとして適当なものを、図 3 の(I)  $\sim$  (VI)の中からそれぞれ選べ.

- (2) 原子 A, B が, それぞれ, 正, 負のイオンである場合に, 電磁波とより強く相互作用するフォノンに対応するのは図 2 の P と Q のどちらであるかを答えよ. また, 相互作用が強くなる理由を 3 行以内で答えよ.

- (3) 2n番目および 2n+1番目の原子の運動方程式は、それぞれ、式(i)、(ii)の形で与えられる.  $\boxed{S}$  ,  $\boxed{T}$  を埋めて、これらの式を完成させよ.

$$m\frac{d^2u_{2n}}{dt^2} = \beta\left(\boxed{S}\right) \tag{i}$$

$$M\frac{d^2u_{2n+1}}{dt^2} = \beta\left(\boxed{T}\right)$$

(ii)

(4) 図 2 の(e)の状態における原子の最大変位を与える概略図を図 3 の(I) ~(VI)の中から選べ. その際、式(i)、(ii)の解として式(iii)、(iv)で与えられる進行波を考えて、 $k=\frac{\pi}{2L}$ の条件において得られる a、b、 $\omega$ の関係式を導出し、選んだ理由を説明せよ。なお、式中のi は虚数単位である.

$$u_{2n} = ae^{-i(\omega t - 2nkL)}$$

(iii)

$u_{2n+1} = be^{-i\{\omega t - (2n+1)kL\}}$  (iv)

- (5) フォノン散乱は、電子の移動度を下げる重要な要因となる。その影響は低温と高温のいずれで顕著となるかを理由を付して答えよ。また、特に高電界中での電子伝導に対して強い影響を与えるのは P, Q のいずれであるかを理由を付して答えよ。

- (6) 一般に、間接遷移型半導体での電子・正孔の再結合過程においてはフォノンが重要な役割を果たす。その理由を波数・エネルギーの観点から5行以内で述べよ。必要なら図を用いてもよい。

### **Problem C**

Consider the one-dimensional lattice model for lattice vibration (phonon) in a solid where atoms A and B are aligned with a distance of L, as shown in Fig. 1. The masses of A and B are m and M, respectively (m < M). Here, the lattice vibration in a transverse mode is considered, and lateral displacements of individual atoms A and B from their equilibrium positions are expressed as  $u_{2n}$  and  $u_{2n+1}$ , respectively, where n is an integer. Each atom receives force only from its nearest neighbors according to Hooke's law with a spring constant of  $\beta$ . For instance, the force acting between the  $(2n)^{th}$  and the  $(2n+1)^{th}$  atom is given by  $\beta(u_{2n+1}-u_{2n})$ . Answer the following questions.

- (1) As for dispersion curves between the angular frequency  $\omega$  and the wavenumber k of the phonon in the transverse mode, we have two branches P and Q as shown in Fig. 2. Choose the appropriate illustrations from (I) to (VI) in Fig. 3 which correspond to the maximum displacements of atoms in the conditions of (c) and (d), respectively, in Fig. 2.

- (2) When atoms A and B are positive and negative ions, respectively, choose the branch for the phonon from P or Q which strongly interacts with an electromagnetic wave. In addition, describe why such an interaction is strong, in three lines or less.

- (3) Equations of motion for the  $(2n)^{th}$  and  $(2n+1)^{th}$  atoms are given by Eqs. (i) and (ii), respectively. Fill in  $\square$  and  $\square$  to complete these equations.

$$m\frac{d^2u_{2n}}{dt^2} = \beta\left(\boxed{S}\right) \tag{i}$$

$$M\frac{d^2u_{2n+1}}{dt^2} = \beta\left(\boxed{\mathsf{T}}\right) \tag{ii}$$

(4) Choose the appropriate illustration from (I) to (VI) in Fig. 3 which corresponds to the maximum displacements of atoms in the condition of (e) in Fig. 2. Explain your answer by supposing traveling waves given by Eqs. (iii) and (iv) as solutions of Eqs. (i) and (ii), and by deriving the relational expressions between a, b and  $\omega$  acquired at the condition of  $k = \frac{\pi}{2L}$ . Here, i in Eqs. (iii) and (iv) is the imaginary unit.

$$u_{2n} = ae^{-i(\omega t - 2nkL)}$$

(iii)

$$u_{2n+1} = be^{-i\{\omega t - (2n+1)kL\}}$$

(iv)

- (5) Phonon scattering is an important factor to degrade electron mobility. Choose the temperature (low or high), at which the phonon scattering effect is significant, and describe the reason for this. On the other hand, the phonon on the P or Q branch strongly influences electron transport in a high electric field. Choose an appropriate branch for this effect and describe the reason why.

- (6) In general, the phonon plays an important role for electron-hole recombination process in an indirect transition semiconductor. Describe the reason for this in five lines or less from the viewpoints of wavenumber and energy. Usage of some illustrations is allowed.

Fig. 3

### 問題D

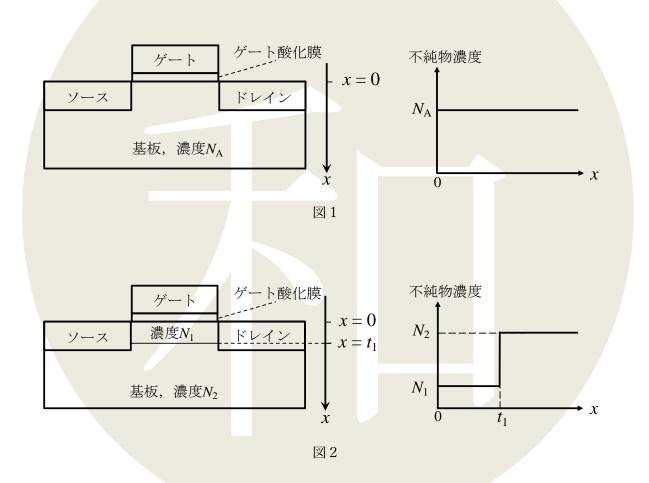

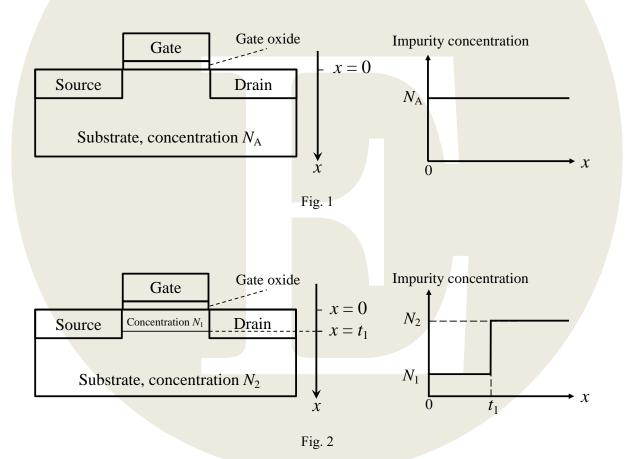

図1と図2のn型MOSトランジスタについて考える.深さ方向にx軸をとり、p型基板とゲート酸化膜の界面をx=0とする.図1のようにトランジスタ1はp型基板に不純物が均一にドープされており、不純物濃度は $N_A$ とする.一方、図2のようにトランジスタ2は、チャネル表面から深さ $t_1$ までは不純物濃度が低く( $0 \le x \le t_1$ で濃度 $N_1$ )、 $t_1$ より深いところで不純物濃度が高くなっている( $x > t_1$ で濃度 $N_2$ ).ゲート酸化膜厚を $t_{ox}$ 、真空の誘電率を $t_{ox}$ 、学体の比誘電率を $t_{ox}$ 、半導体の比誘電率を $t_{ox}$ 、ゲート電圧を $t_{ox}$ 、フラットバンド電圧を $t_{ox}$ 、電子の電荷を $t_{ox}$ とする。界面準位の影響と短チャネル効果は無視する。ソース、ドレイン、および基板は接地されているものとする。

まず、トランジスタ1について次の問に答えよ.

- (1) 正のゲート電圧を大きくしていくとゲート直下の基板中に空乏層が広がる. この空乏層 部分におけるポアソンの方程式をたて,空乏層中の電界Eとポテンシャル $\phi$ の式をxの関数として求めよ. ただし,空乏層幅を $W_d$ とする.

- (2) ゲート電圧をさらに大きくしていくと、あるところで空乏層はそれ以上広がらなくなる. その理由を 2 行程度で説明せよ.

- (3) 最大空乏層幅を $W_{\rm dmax1}$ とする。表面ポテンシャル $\phi_{\rm S}$ が $2\phi_{\rm F}$ に達したときに、空乏層は $W_{\rm dmax1}$ に達することが知られている。この $\phi_{\rm F}$ の定義を述べよ。

- (4) W<sub>dmax1</sub>の式を求めよ.

- (5) このトランジスタのしきい値電圧 $V_{th1}$ を $N_A$ ,  $W_{dmax1}$ を用いて表せ.

- (6) ゲート電圧が $V_{th1}$ に等しいとき、横軸を深さxとして空乏層中の電界Eおよびポテンシャル $\Phi$ をそれぞれ図示せよ.

次に、トランジスタ2について次の問に答えよ.

- (7) 正のゲート電圧を印加するとゲート直下の基板中に空乏層が広がるが、条件によって空 乏層が濃度 $N_1$ の低濃度領域にとどまる場合と、濃度 $N_2$ の高濃度領域に達する場合がある。 それぞれの場合について、この空乏層部分におけるポアソンの方程式をたて、空乏層中 の電界Eとポテンシャル $\phi$ の式をxの関数として求めよ。問(1)と同様に、空乏層幅を $W_d$ と する.

- (8) 空乏層が最大になったときに空乏層が濃度 $N_2$ の高濃度領域に達するための $t_1$ の条件を不等式で示せ.

以下では、問(8)の条件が満たされているものとする.

- (9) 最大空乏層幅 $W_{\rm dmax2}$ を式で示せ.

- (10)トランジスタ2のしきい値電圧 $V_{th2}$ を $N_1$ ,  $N_2$ ,  $t_1$ ,  $W_{dmax2}$ を用いて表せ.

- (11)ゲート電圧が $V_{\text{th2}}$ に等しいとき、横軸を深さxとして空乏層中の電界Eおよびポテンシャル $\Phi$ をそれぞれ図示せよ.

- (12)以上の結果から、トランジスタ 1 とトランジスタ 2 の最大空乏層幅について考える。  $N_2\gg N_1$ とすると、 $V_{\rm th1}=V_{\rm th2}$ の条件で $W_{\rm dmax2}$ が $W_{\rm dmax1}$ よりも小さくなるように設計することができる。 どのようにすれば $W_{\rm dmax2}< W_{\rm dmax1}$ とできるかを 5 行程度で定性的に述べよ。 図を用いてもよい。

#### **Problem D**

Consider the n-type MOS transistors shown in Figs. 1 and 2. Take the x axis in the depth direction with x = 0 at the interface between the p-type substrate and the gate oxide. In Transistor 1, the impurities are uniformly doped in the p-type substrate and the impurity concentration is  $N_A$ , as shown in Fig. 1. In Transistor 2, on the other hand, the impurity concentration from the surface to a depth of  $t_1$  is low (concentration of  $N_1$  in  $0 \le x \le t_1$ ) and the impurity concentration is high in the deeper region (concentration of  $N_2$  in  $x > t_1$ ), as shown in Fig. 2. The gate oxide thickness is  $t_{ox}$ , the permittivity of vacuum is  $\varepsilon_0$ , the relative permittivity of the gate oxide is  $\varepsilon_{ox}$ , the relative permittivity of the semiconductor is  $\varepsilon_{Si}$ , the gate voltage is  $V_G$ , the flat band voltage is  $V_{FB}$ , and the electron charge is q. The effect of the interface states and the short channel effect are negligible. Assume that the source, drain, and substrate are grounded.

First, answer the following questions on Transistor 1.

- (1) On increasing the positive gate voltage, the depletion layer below the gate expands into the substrate. Solve the Poisson equation in the depletion region in the substrate and obtain the electric field E and the potential  $\varphi$  as functions of x. Here, the depletion width is  $W_d$ .

- (2) As the gate voltage is increased further, the depletion layer does not expand any more at a certain point. Explain the reason for this in about two lines.

- (3)  $W_{\rm dmax1}$  is defined as the maximum depletion width. It is known that the depletion region reaches  $W_{\rm dmax1}$  when the surface potential  $\phi_{\rm S}$  reaches  $2\phi_{\rm F}$ . Explain the definition of  $\phi_{\rm F}$ .

- (4) Obtain the formula of  $W_{\text{dmax}1}$ .

- (5) Express the threshold voltage  $V_{\text{th}1}$  of Transistor 1 using  $N_{\text{A}}$  and  $W_{\text{dmax}1}$ .

- (6) Draw schematic figures of the electric field E and the potential  $\phi$  with a horizontal axis of x when the gate voltage is  $V_{\text{th}1}$ .

Next, answer the following questions on Transistor 2.

- (7) On increasing the positive gate voltage, the depletion layer below the gate expands into the substrate. Depending on the conditions, the depletion region remains in the low concentration region with  $N_1$ , or the depletion region reaches the high concentration region with  $N_2$ . In each case, solve the Poisson equation in the depletion region in the substrate and obtain the electric field E and the potential  $\Phi$  as functions of E. As in Question (1) the depletion width is expressed as E

- (8) Express an inequality to show the condition of  $t_1$  for the maximum depletion width to reach the high concentration region with  $N_2$ .

Assume that the condition in Question (8) is satisfied in the following questions.

- (9) Obtain the formula of the maximum depletion width  $W_{\rm dmax2}$ .

- (10) Express the threshold voltage  $V_{\text{th}2}$  using  $N_1$ ,  $N_2$ ,  $t_1$ , and  $W_{\text{dmax}2}$ .

- (11) Draw schematic figures of the electric field E and the potential  $\phi$  with a horizontal axis of x when the gate voltage is  $V_{\text{th}2}$ .

- (12) Based on the results of above questions, let us consider the maximum depletion width of Transistor 1 and Transistor 2. When  $N_2 \gg N_1$ ,  $W_{\rm dmax2}$  can be designed to be smaller than  $W_{\rm dmax1}$  at the condition of  $V_{\rm th1} = V_{\rm th2}$ . Explain qualitatively in about five lines how to realize  $W_{\rm dmax2} < W_{\rm dmax1}$ . Usage of figures is allowed.

# 問題E

6極の三相誘導機がある. 50 Hz の三相電源に接続し電動機として駆動する. 定格運転時に 1分あたり 960 回転で動作しており、その機械出力は 6kW である. この電動機の無負荷損失は 200 W であり、この損失は定格運転時も変化しないものとする. また、この電動機の鉄損は十分小さく無視できる. 一次抵抗と一次側から見た二次側の抵抗の比は 4:5 である. この誘導電動機の動作について、以下の間に答えよ.

- (1) この電動機の単相 T 形等価回路を図示せよ. ただし必要な回路定数は自分で定義せよ. そしてそれらの回路定数の意味を説明せよ.

- (2) この電動機の同期回転数は1分あたり何回転か求めよ.

- (3) 定格運転時のすべりを求めよ.

- (4) 定格運転時の二次回路に流れる電流の周波数を求めよ.

- (5) 定格運転時の三相二次電力を求めよ.

- (6) 定格運転時の機械トルクを求めよ.

- (7) 定格運転時におけるこの誘導電動機のエネルギーの流れを図示し説明せよ. それをもとに、この電動機の定格運転時の効率を求めよ.

ここまでは、すべりが 0 と 1 の間の電動機としての動作を議論した。次に、この誘導機のより一般的な動作について考える。

(8) すべりが1を超える場合,すべりが1と0の間の値を取る場合,すべりが負の値になる場合の回転子の回転速度と発生トルクとの関係をひとつのグラフとして図示せよ.また,各々の場合の電気機械エネルギー変換機能とそのエネルギーの流れについて説明せよ.

#### Problem E

There is a six-pole three-phase induction machine. The induction machine is connected to a three-phase power source of 50 Hz, and operated as a motor. Under nominal operation conditions, the rotary speed is 960 revolutions per minute (rpm) and the mechanical output is 6 kW. The noload loss of the motor is 200 W and the amount of the loss is assumed unchanged under nominal operation conditions. The iron loss of the motor is negligibly small. The ratio of the primary resistance to the secondary resistance seen from primary side is 4:5. Answer the following questions concerning the operation of the induction motor.

- (1) Draw a single-phase T-type equivalent circuit of the motor. Define necessary circuit constants by yourself. Explain the meanings of the circuit constants.

- (2) Find the synchronous rotary speed per minute of the motor.

- (3) Find the slip under the aforementioned nominal operation conditions.

- (4) Find the frequency of the current flowing in the secondary circuit under the nominal operation conditions.

- (5) Find the three-phase secondary power under the nominal operation conditions.

- (6) Find the mechanical torque under the nominal operation conditions.

- (7) Illustrate the energy flow in the induction motor under the nominal operation conditions and explain your illustration. Find the efficiency of the motor under the nominal operation conditions based on the illustration.

In the previous questions, a motor with slip between 0 and 1 was discussed. In the following, consider more general operation of the induction machine.

(8) Draw a graph representing the relationship between rotary speed of the rotor and torque in the following three modes: When the slip is larger than 1, when the slip is between 1 and 0, and when the slip is negative. Explain the function of the electro-mechanical energy conversion and the energy flow in each mode.

# 問題F

電力システムにおいて、発電機 1 と発電機 2 の 2 台の同期発電機が、共通の基準周波数である  $f_0=50$  Hzの近傍で同期運転している。本電力システムにおいて送配電ロスはないものとする。時刻 t<0 sにおいては、負荷の大きさは  $P_L=320$  MWで一定であり、基準周波数からの偏差は $\Delta f=0$  Hzであった。時刻 t=0 sにおいて、負荷がステップ状に30 MW増加し、時刻 t>0 sにおいては、負荷の大きさは  $P_L=350$  MWで一定となった。発電機 1 および発電機 2 のそれぞれについて、機械入力、電気出力と周波数の関係を表す常微分方程式は下記の通りとなる。ただし、発電機 1 、発電機 1 の慣性定数をそれぞれ1 、1 、機械入力をそれぞれ1 、1 、1 、程電機 1 、程電機 1 、最高に対して、表面に対して、

$$M_1 \frac{df}{dt} = P_{\rm m1} - P_{\rm e1}$$

$$M_2 \frac{df}{dt} = P_{\rm m2} - P_{\rm e2}$$

また、各発電機の慣性定数および定格出力を以下の値とする.

発電機1

慣性定数 :  $M_1 = 40 \text{ MW} \cdot \text{s}^2$

定格出力 : PR<sub>1</sub>=400 MW

発電機2

慣性定数 :  $M_2 = 20 \,\mathrm{MW} \cdot \mathrm{s}^2$

定格出力 : PR<sub>2</sub>=200 MW

以下の間に答えよ.

(1) この電力システムにおいて、発電機 1 および発電機 2 を用いて周波数偏差に対する比例制御を行うものとする。ただし、ここでの比例制御とは、t=0 s 以降における周波数偏差 $\Delta f$  と機械入力の変化 $\Delta P_{m1}$ 、 $\Delta P_{m2}$  および比例ゲイン $1/r_1$ 、 $1/r_2$ の間に下記の関係が成り立つものである。

$$\Delta P_{\text{m1}} = -\Delta f/r_1$$

,  $r_1 = 0.005 \text{ (MW)}^{-1} \text{s}^{-1}$

$$\Delta P_{\text{m2}} = -\Delta f/r_2$$

,  $r_2 = 0.01 \text{ (MW)}^{-1} \text{s}^{-1}$

このとき、周波数偏差 $\Delta f$ の $t \ge 0$  sにおける時間変化を求め、無限の時間が経過したのちに、周波数が基準値に回復しないことを示せ、

- (2) この電力システムにおいて、発電機 1 を用いて周波数偏差に対する PI 制御を行うものとする. すなわち、問(1)で述べた比例制御に加え、ゲイン $K_I=240$  MWの積分制御を行う. 一方、発電機 2 については、問(1)で述べた比例制御のみを行うものとする. このとき、周波数偏差 $\Delta f$  の $t \geq 0$  sにおける時間変化を求め、無限の時間が経過したのちに、周波数が基準値に回復することを示せ.

- (3) 間(2)で発電機 1 を用いて PI 制御を行う者が、式(i)で計算される報酬を受け取るものとし、 $\alpha$ は実定数とする。t=10 sまでの報酬を求めよ。ただし、 $\alpha$ にかかる係数の有効数字を 2 桁とせよ。また、この発電機 1 の燃料費が式(ii)で表されるものとし、a,b は正の実定数とする。この報酬が、t=0 s から t=10 s までの機械入力の増加分  $\Delta P_{m1}$ に伴う燃料費の増加分を上回るための条件を、 $\alpha$ 、 $\alpha$ 、 $\alpha$ 0のうち必要なものを用いて表せ。

発電機

$$1 \circ t$$

秒までの報酬 : Reward =  $\alpha \int_0^t \Delta P_{m1} dt$  (i)

発電機

$$1$$

の単位秒当たりの燃料費  $F(P_{m1}) = aP_{m1} + b$  (ii)

(4) 今日,太陽光発電などの再生可能エネルギー電源の大量導入に伴い,周波数制御の需要が急速に増加している.この点と,問(3)の内容を踏まえ,電力システムにおける周波数の安定性を維持するための対応策を簡潔に説明せよ.

### **Problem F**

In a power system, two synchronous generators, Generator 1 and Generator 2, are under synchronized operation around the common standard frequency  $f_0 = 50$  Hz. The energy losses in transmission and distribution networks are assumed to be zero in this power system. When t < 0 s, the load is constant at  $P_L = 320$  MW, and the deviation in frequency from the standard value is  $\Delta f = 0$  Hz. At t = 0 s, the load makes a step increase of 30 MW, and is kept constant at  $P_L = 350$  MW when t > 0 s. The ordinary differential equations of the mechanical inputs, the electrical outputs and the frequency are described as follows. Here, the inertia constants of Generator 1 and Generator 2 are denoted as  $M_1$  and  $M_2$ , respectively. The mechanical inputs of Generator 1 and Generator 2 are denoted as  $P_{m1}$  and  $P_{m2}$ , respectively. The electrical outputs of Generator 1 and Generator 2 are denoted as  $P_{e1}$  and  $P_{e2}$ , respectively. The frequency f is common for the both generators.

$$M_1 \frac{df}{dt} = P_{\rm m1} - P_{\rm e1}$$

$$M_2 \frac{df}{dt} = P_{\rm m2} - P_{\rm e2}$$

Values of the inertia constants and the rated outputs are listed as follows.

Generator 1

Inertia constant :  $M_1 = 40 \text{ MW} \cdot \text{s}^2$

Rated output :  $PR_1 = 400 \text{ MW}$

Generator 2

Inertia constant :  $M_2 = 20 \text{ MW} \cdot \text{s}^2$

Rated output :  $PR_2 = 200 \text{ MW}$

Answer the following questions.

(1) We assume that Generator 1 and Generator 2 are used for proportional control of the frequency deviation in this power system. Here, the proportional control means that the following relationships hold between the frequency deviation  $\Delta f$ , changes in the mechanical inputs  $\Delta P_{m1}$

and  $\Delta P_{\rm m2}$ , and gains in the proportional control  $1/r_1$  and  $1/r_2$  when  $t \ge 0$  s.

$$\Delta P_{\text{m1}} = -\Delta f/r_1, \ r_1 = 0.005 \ (\text{MW})^{-1} \text{s}^{-1}$$

$\Delta P_{\text{m2}} = -\Delta f/r_2, \ r_2 = 0.01 \ (\text{MW})^{-1} \text{s}^{-1}$

Taking the above conditions into consideration, find an expression for  $\Delta f$  when  $t \ge 0$  s, and show that the frequency does not converge to the standard frequency after infinite time has passed.

- (2) We assume that Generator 1 is used for a proportional-integral control of the frequency deviation in this power system; in addition to the proportional control described in Question (1), an integral control with a gain of  $K_I = 240\,$  MW is applied. On the other hand, Generator 2 is used only for the proportional control described in Question (1). Taking this condition into consideration, find an expression for  $\Delta f$  when  $t \geq 0$  s, and show that the frequency converges to the standard frequency after infinite time has passed.

- (3) We assume that the operators of Generator 1 in Question (2), which is used for the proportional-integral control, receive a revenue calculated by Equation (i), in which  $\alpha$  is a real constant. Find the revenue until t = 10 s using two significant figures for the coefficient of  $\alpha$ . Furthermore, the fuel cost of Generator 1 is expressed by Equation (ii), in which a and b are positive real constants. Find also the condition, using some of  $\alpha$ , a and b, for this revenue to be higher than the increase in the fuel cost accompanying the increase in the mechanical input  $\Delta P_{m1}$  from t = 0 s to t = 10 s.

Revenue until

$$t$$

[s] of Generator 1 : Reward =  $\alpha \int_0^t \Delta P_{m1} dt$  (i)

Fuel cost per second of Generator 1 :  $F(P_{m1}) = \alpha P_{m1} + b$  (ii)

(4) Nowadays, the demand of frequency control is increasing rapidly due to large scale integration of renewable energy sources such as solar power generation. Taking this point and the contents of Question (3) into consideration, briefly explain measures to maintain the stability of frequency in power systems.